SI、PI、EMC、CAE、DFM、全面的なシミュレーションと設計

十分に設計性と製造性を考慮したシミュレーション解析

シニアエンジニアからのフルテクニカルサポート、結果の正確性と信頼性を確保

DDRx、PCIE、SATA、SAS、SFP... 豊富な経験を持ち

GHz級の信号も対応可能

Introduction

SI、PI、EMC、CAE、DFM、全面的なシミュレーションと設計

十分に設計性と製造性を考慮したシミュレーション解析

シニアエンジニアからのフルテクニカルサポート、結果の正確性と信頼性を確保

DDRx、PCIE、SATA、SAS、SFP... 豊富な経験を持ち

GHz級の信号も対応可能

SI

Siganl Integrity Analysis

プリ(デザインルール、トポロジー)ポスト(反射、クロストーク、タイミング)マルチボードシステムの共同解析

PI

Power Integrity Analysis

DC電圧降下解析、プレーン共振解析、PDNインピーダンス、デカップコンデンサ最適化

EMC

Electro Magnetic Compatibility

EMC設計、EMC改善、EMCテスト

DMF

Power Integrity Analysis

DFF製造可能性、DFA組立て可能性、DFTテスト可能性

Signal Integrity Analysis

√ IBISモデル、Hspiceモデル、Sパラメータ対応

√ Frequency domain、Time domainなど様々なシミュレーション手段

√ クロストーク、リンギング、ジッター、エラーレートを考慮

√ DDR3、PICEなど多くの実績があり、豊富な経験を持つ

遅延計算

トポロジー解析

反射シミュレーション

インピーダンス計算

クロストークシミュレーション

層構成解析

タイミング解析

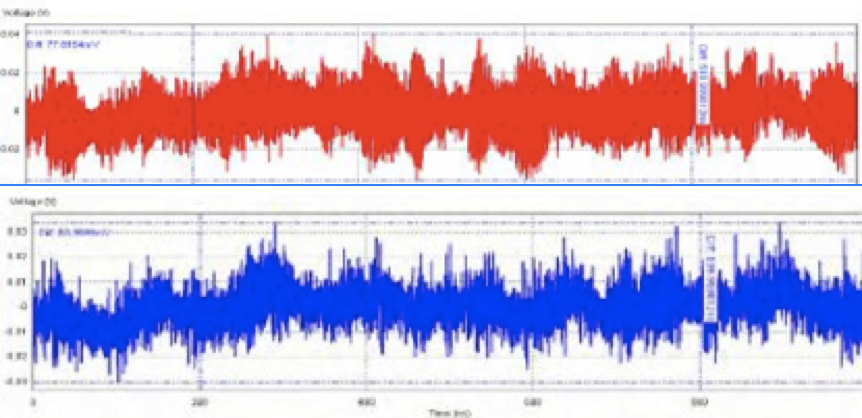

SSNシミュレーション

Sパラメータ抽出

シリアル・パラレルリンク

Power Integrity Analysis

DC IR Drop / DC電圧降下解析

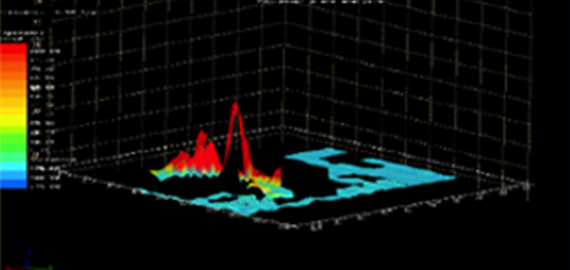

Plane Resonance / プレーン共振解析

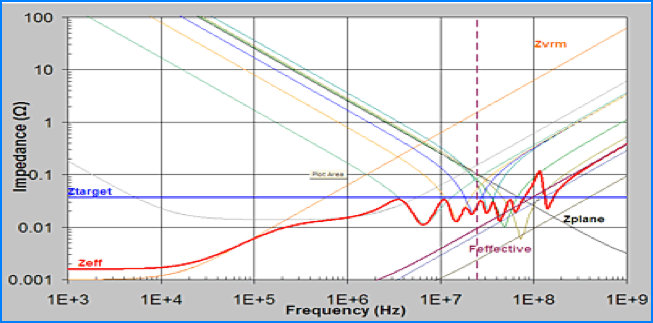

PDN lmpedance / PDNインピーダンス解析

Decouping cap.optimization / デカップコンデンサ最適化

Electro Magnetic Compatibility

電磁両立性は電磁妨害(EMI)と電磁敏感度(EMS)という二つの部分を含んでいます。ボードグレードEMC設計は源からコントロールという考えで、設計段階からSI分析に合わせて、根本的にEMC問題を解決するように対策を取ります。外部インターフェースを持つ片面基板や完全なシールドが出来ない製品に対し、ボードグレードEMC設計は他のEMC対策で代えられない存在です。片面基板に対するEMC設計考慮は後工程のプレッシャーを軽減出来ると同時に開発サイクル短縮、ロットコスト削減を実現出来ます。

EMC設計

EMC設計

ユーザ様が製品EMCテストで発見した問題に対して主にノイズ発生源、敏感設備、カップリング方式という三つのファクターから取り掛かり、実際にテストで出た問題に合わせて改善案を提出し、改善を行います。

EMC設計

ユーザ様と協力して、製品の一連の電磁両立性テストを行います、途中出た問題に対し、参考にアドバイスを出します。

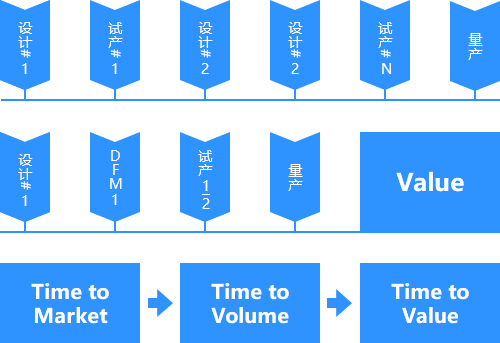

Design for Manufaturing

DFM製造性解析とは設計段階において製品の製造性と組立性などのファクターを考慮し、最低コスト、最短時間、最高の品質を実現するということです。DFMはコンカレンとーエンジニアリングにおけるコア技術で、主に設計情報の工程分析、製造合理性判定、改善設計提案を行います。我々は製造向けのシミュレーションシステムを通じて、設計チームと歩調を合わせることを実現し、設計、製造から実装までの全過程シミュレーション解析が実施できます。DFMコンセプトの設計方法で、有効的に試作回数を減らし、開発サイクルを短縮できます。

Signal quality Analysis

Design for Fabrication

Design for Testability

Design for Assembly

DFM

√ 開発期間を短縮、改版回数及び手戻りを低減

√ 試作回数を減らして、生産コストを削減

√ 工程の標準化管理より、品質アップと信頼性を向上

√ 複雑な基板製造フローを簡単に、生産能力を高め